4G&5G小基站解决方案

利用开源系统平台和硬件来研究小型的基站,是无线电和LTE无线通信领域研究的一个重要方向。传统的商用基站设备昂贵,研发周期长,操作复杂度高,更改功能繁琐。针对在LTE无线通信基站研究过程中,传统的基站更改功能复杂,研发周期长的问题,方案提出了采用开源的OAI 5G和srsRAN软件系统和软件无线电硬件平台来搭建实时运行的基站及和终端交互的研究方法。这个方法避免了笨重昂贵的基站来长周期的研发基站问题,提高了研究基站及和终端交互的效率。

1. 功能描述

基于SDR-LW/USRP-LW系列的软件无线电硬件,结合srsRAN、OpenAirInterface(OAI)5G等软件平台,可以实现4G/5G模拟基站 和终端的搭建。通过使用不同型号的软件无线电硬件和不同的基站配置参数,可以实现不同的功能。

本系统可以完全模拟端到端协议栈,完全模拟基站、终端、核心网,同时满足对应的3GPP协议规范。支持与商用设备对接(商用终端、商用核心网),支持基于协议栈的二次开发。

(1)SDR设备将上位机处理的数字信号通过射频前端转换成模拟信号,经由空中接口发射出去;

(2)srsRAN/OAI实现协议栈功能,从物理层到网络层的功能实现,根据不同的试验可以编译相应的模块。

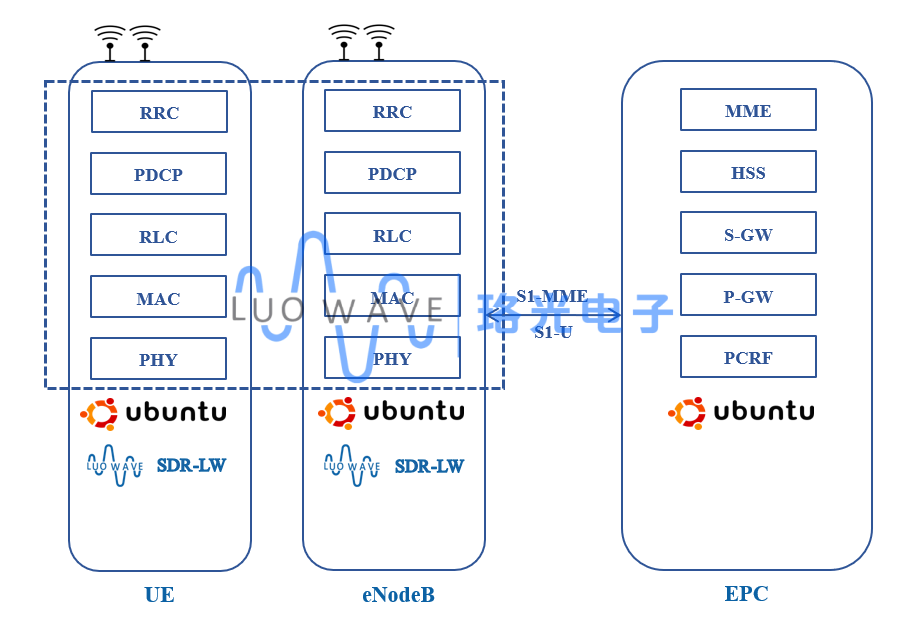

图1 LTE系统结构图

图1是LTE系统结构图,包括核心网(EPC),基站(eNB)和用户(UE)三部分,各部分按照3GPP LTE协议栈实现相应的功能。

UE侧包含PHY,MAC,RLC,PDCP,RRC等功能,UE侧通过空中接口和eNB侧进行上下行数据交互;中间是eNB的架构图,与UE的空中接口,以及与核心网的S1-U和S1-MME接口;右侧是EPC,主要由MME和S-GW、P-GW等网元组成。

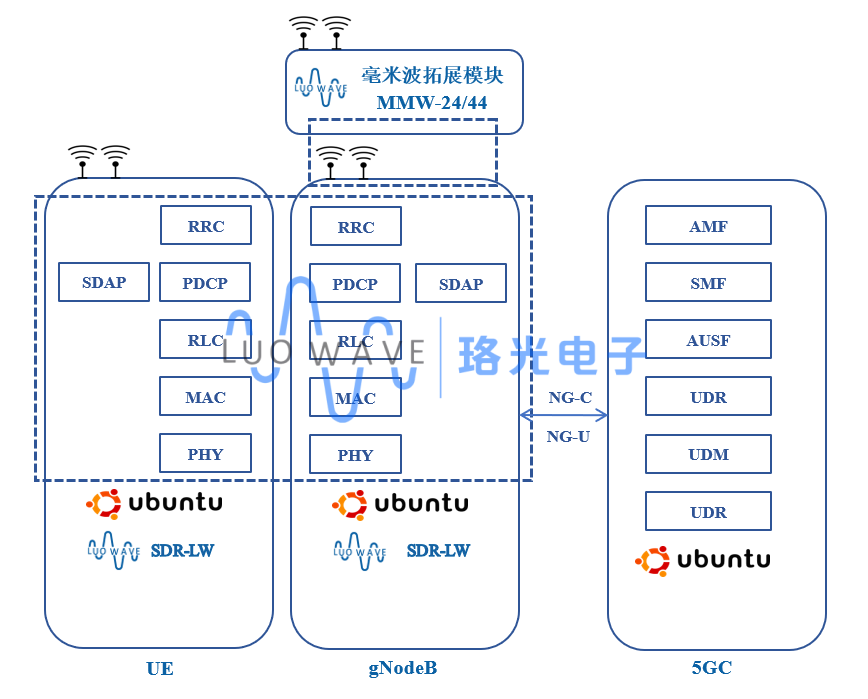

图2 NR系统结构图

图2是NR系统结构图,5G的无线接口继承了4G协议栈,仅用户面增加了一层SDAP层,用来标记QoS(Quality of Service,服务质量)。5G系统架构同样分为三个部分:用户(UE),5G基站(gNodeB),核心网(5GC)。ng-eNB、gNodeB和5GC通过NG接口相连接。

2. 实物搭建图

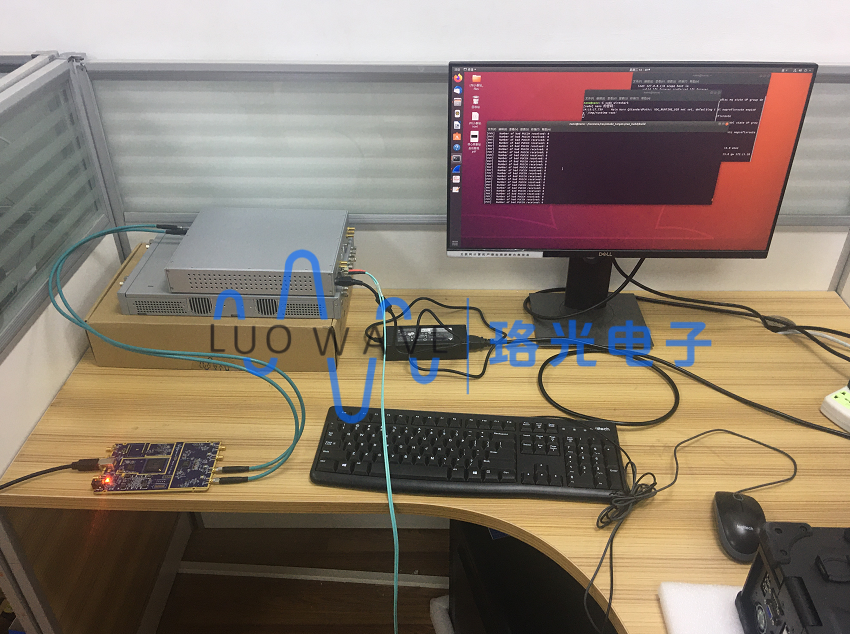

图3 USRP-LW B210模拟终端+ USRP-LW N310模拟基站

图4 商用终端+ USRP-LW N321模拟基站(连接天线)

3. 软件界面图

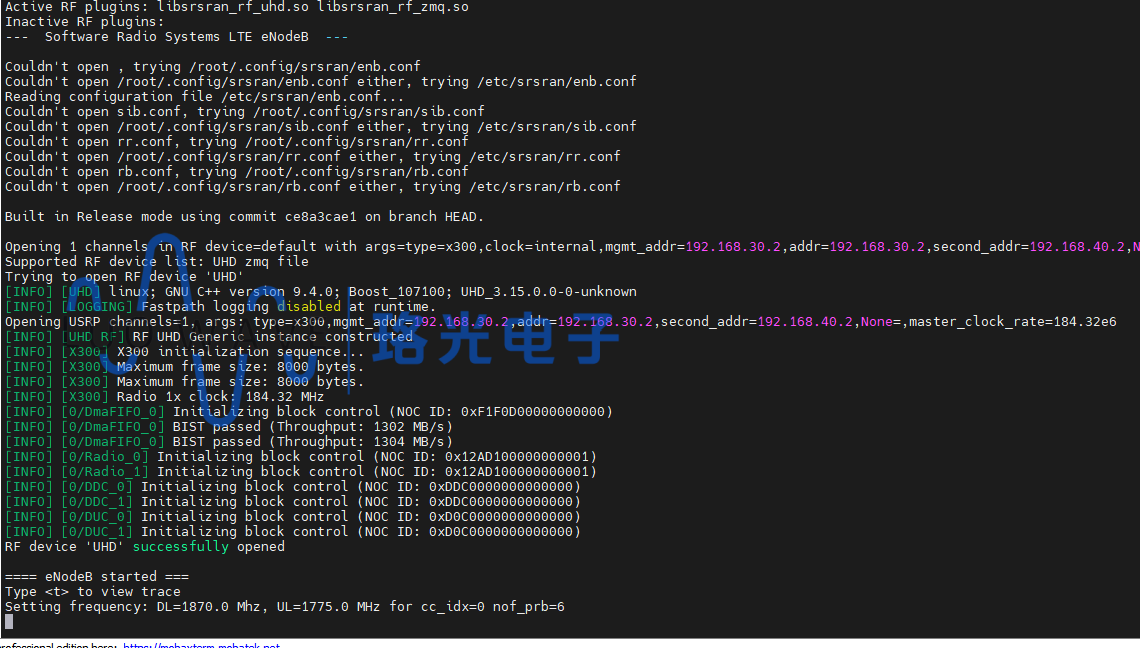

图5 运行4G基站(基于srsRAN+ USRP-LW X310搭建)

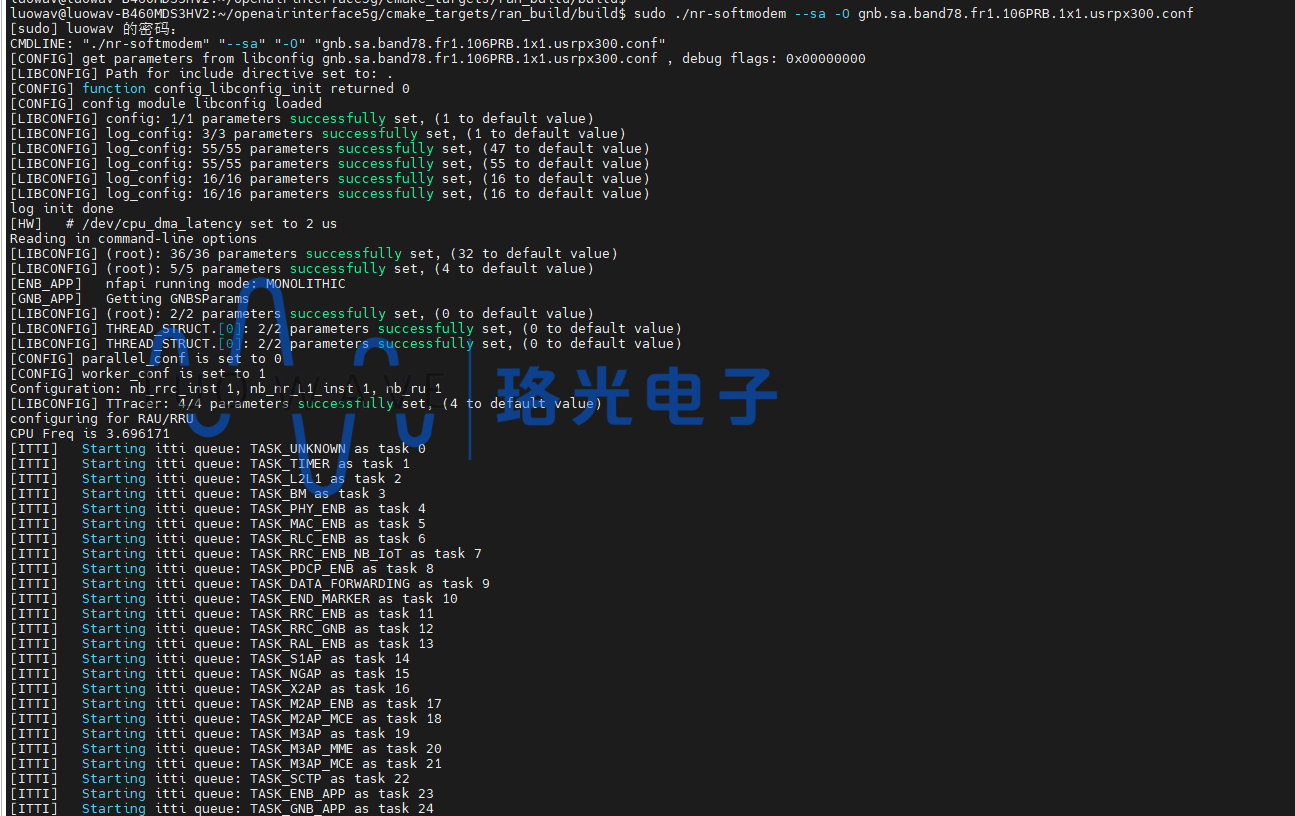

图6 运行5G基站(基于OAI 5G + USRP-LW X310搭建)

4. 构建OAI系统

构建OpenAirInterface (OAI) 系统涉及到硬件选择、软件配置安装以及配置各种网络参数。

基本步骤为:

| 1 | 准备硬件 | 选择合适的SDR-LW/USRP-LW设备 |

| 2 | 系统安装 | 安装Ubuntu LTS操作系统 |

| 3 | 安装依赖 | 根据OAI文档,安装所有必要的软件依赖 |

| 4 | 下载源码 | 从OAI官方GitHub获取OAI源代码 |

| 5 | 代码编译 | 构建eNodeB、EPC或其他组件,涉及配置CMake,然后编译源代码 |

| 6 | 配置系统 | 设置OAI配置文件,包括指定IP地址、子网、RF参数、认证信息等 |

| 7 | 启动系统 | 首先启动EPC组件(如HSS、MME、SPGW),然后启动eNodeB |

| 8 | 接入测试 | 使用OAI提供的工具和日志进行调试,确保系统按预期运行,并与UE(商用5G终端)正确通信 |

5. 推荐硬件型号

型号 | |||

频率范围 | 70MHz-6GHz | 10MHz-6GHz | 1MHz-7.2GHz |

通道数 | 2 | 2 | 4 |

最大实时带宽 | 56MHz | 160MHz | 400MHz |

FPGA | Xilinx Artix-7 XC7A200T | Xilinx Kintex-7 XC7K410T | Xilinx Zynq Ultrascale+ZU28DR RFSoC |

ADC分辨率 | 12bits | 14bits | 12bits |

DAC分辨率 | 12bits | 16bits | 14bits |

板载处理器 | Intel i7 8700,主频3.2GHz,6核心, 12线程 | Intel i7 9700,主频 3.0GHz,8核心, 8线程 | Intel i9 9900K,主频 3.6GHz,8核心, 16线程 |

内存 | 16G DDR4 | 16G DDR4 | 32G DDR4 |

SSD | 500G | 500G | 500G |

USB | USB 3.0*4 | USB 3.0*4 | USB 3.0*4 |

有线网口 | 1Gbps RJ45网口 | 1Gbps RJ45网口*2 | 1Gbps RJ45网口*2 |

光口 | - | 双口10Gbps SFP+接口 | 100Gbps或4*10Gbps QSFP28接口 |

PCIe | - | PCIe Gen2*4 | - |

编程接口 | JTAG | JTAG | JTAG |

物理尺寸 | 23.5*30*8.5 cm | 23.5*26.5*13.5 cm | 43*37.8*14.5 cm |

重量 | 2.8kg | 9.5kg | 13.6kg |

6. 典型应用场景

- 部署专属网络;

- 用于教学科研,研究基站、终端运行结构和协议等;

- 开发测试产品,如替代CMW500的一些测试功能;

- 基于协议栈的算法验证和二次开发。